![PDF] Differential static ultra low-voltage CMOS flip-flop for high speed applications | Semantic Scholar PDF] Differential static ultra low-voltage CMOS flip-flop for high speed applications | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/aba79f96f2b565b16da053c8c3795311997eedba/3-Figure3-1.png)

PDF] Differential static ultra low-voltage CMOS flip-flop for high speed applications | Semantic Scholar

![PDF] Ultra Low-voltage Differential Static D Flip-Flop for High Speed Digital Applications | Semantic Scholar PDF] Ultra Low-voltage Differential Static D Flip-Flop for High Speed Digital Applications | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/6d958b214082ca238aca03316861f3a06ccc35b2/2-Figure2-1.png)

PDF] Ultra Low-voltage Differential Static D Flip-Flop for High Speed Digital Applications | Semantic Scholar

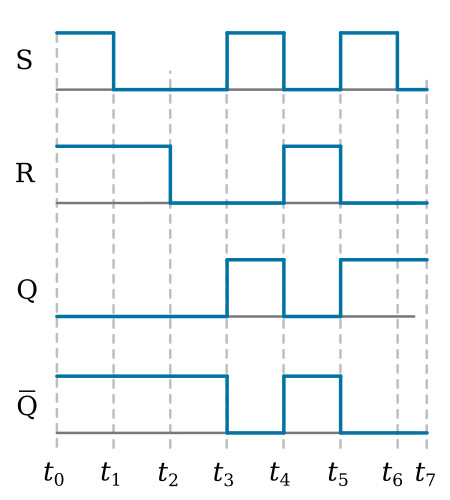

Simulated waveform of the differential RZ-to-NRZ SR-latch IC at 1 Gb/s... | Download Scientific Diagram

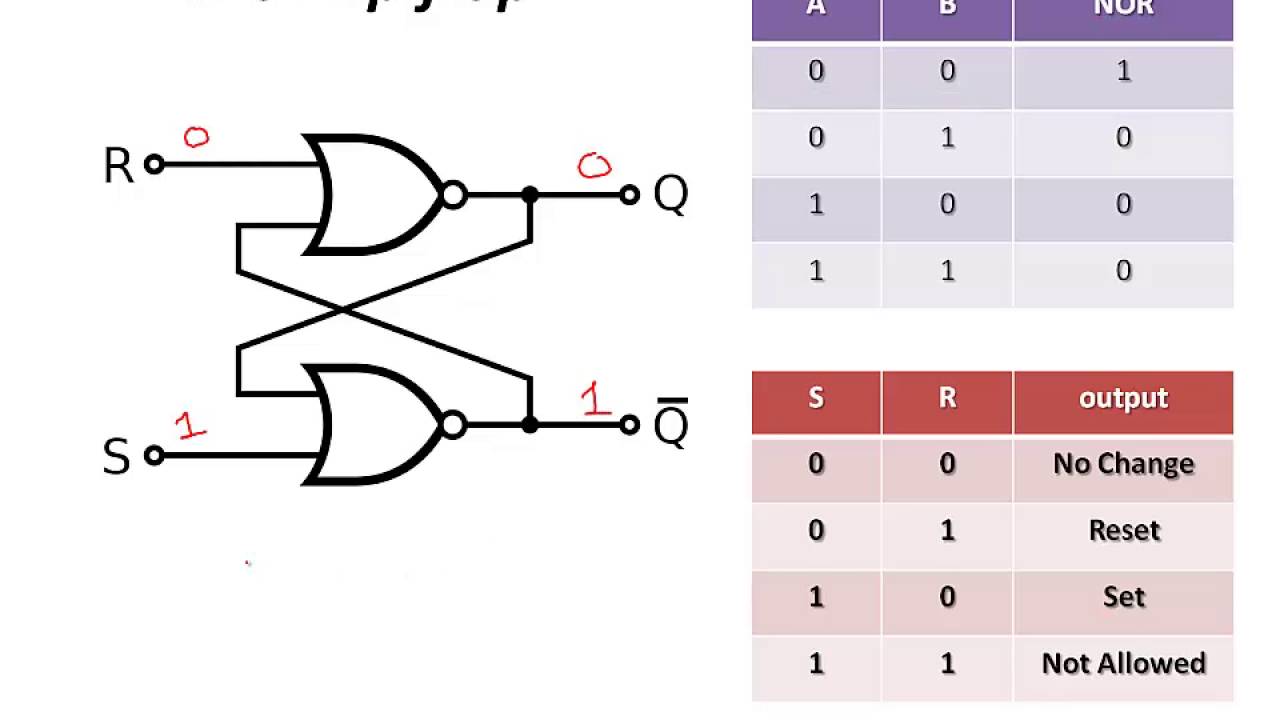

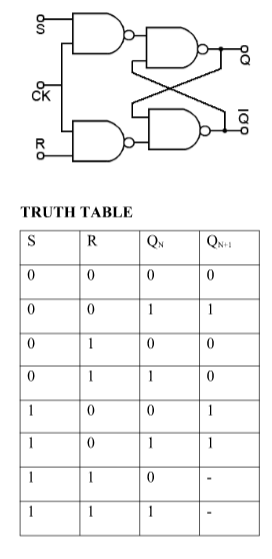

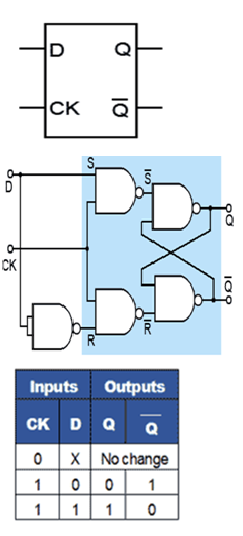

JK Flip-Flop Explained | Race Around Condition in JK Flip-Flop | JK Flip- Flop Truth Table, Excitation table and Timing Diagram - ALL ABOUT ELECTRONICS

![PDF] Ultra Low-voltage Differential Static D Flip-Flop for High Speed Digital Applications | Semantic Scholar PDF] Ultra Low-voltage Differential Static D Flip-Flop for High Speed Digital Applications | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/6d958b214082ca238aca03316861f3a06ccc35b2/3-Figure5-1.png)

PDF] Ultra Low-voltage Differential Static D Flip-Flop for High Speed Digital Applications | Semantic Scholar

![PDF] Ultra Low-voltage Differential Static D Flip-Flop for High Speed Digital Applications | Semantic Scholar PDF] Ultra Low-voltage Differential Static D Flip-Flop for High Speed Digital Applications | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/6d958b214082ca238aca03316861f3a06ccc35b2/5-Figure10-1.png)

PDF] Ultra Low-voltage Differential Static D Flip-Flop for High Speed Digital Applications | Semantic Scholar

![PDF] Ultra Low-voltage Differential Static D Flip-Flop for High Speed Digital Applications | Semantic Scholar PDF] Ultra Low-voltage Differential Static D Flip-Flop for High Speed Digital Applications | Semantic Scholar](https://d3i71xaburhd42.cloudfront.net/6d958b214082ca238aca03316861f3a06ccc35b2/1-Figure1-1.png)